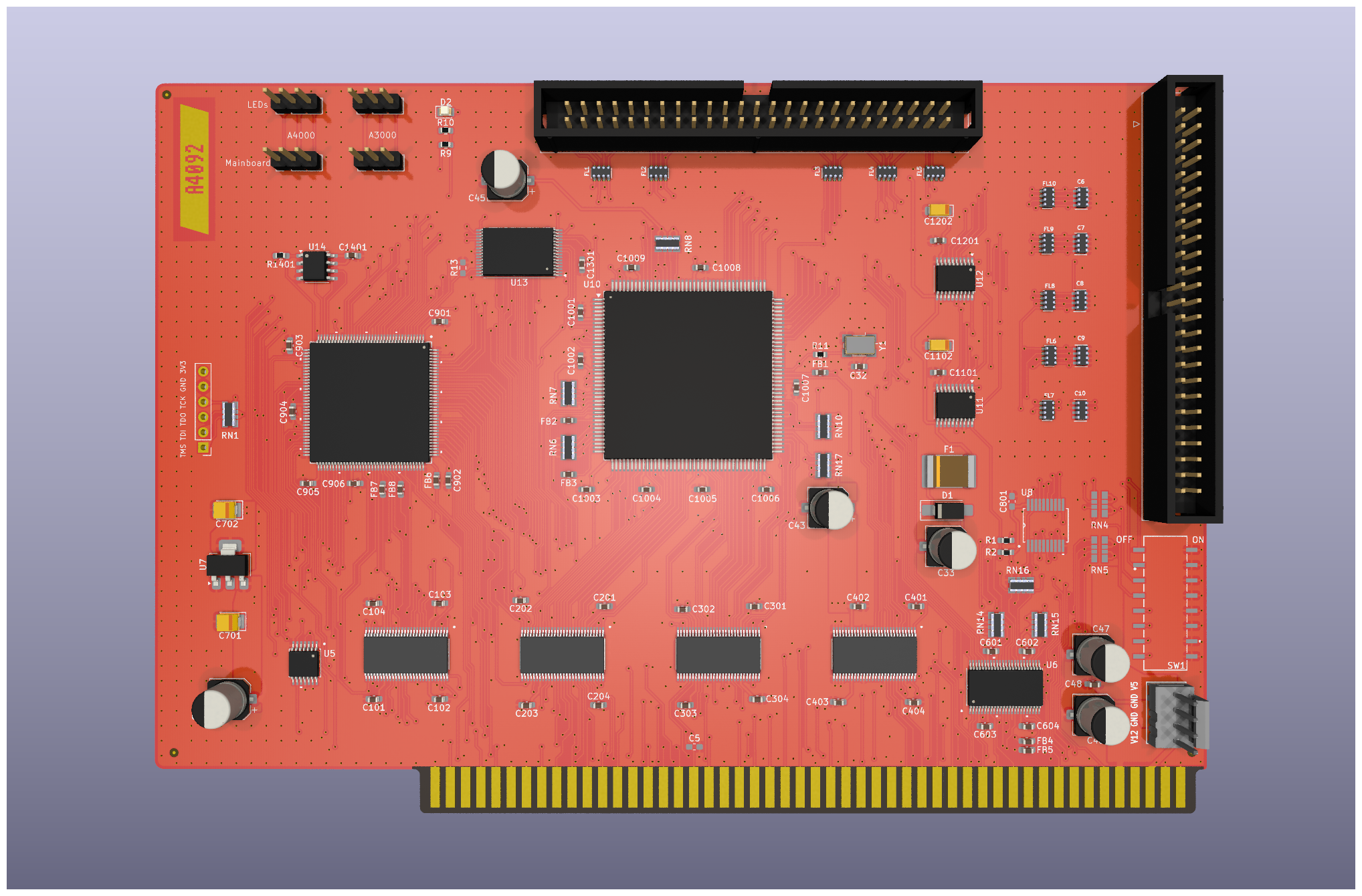

mirror of

https://github.com/LIV2/A4092-dev.git

synced 2025-12-06 00:32:49 +00:00

*_region was matching when slave_cycle was true but without checking that the base address matched - this would cause these regions to match when other Z3 boards are being accessed

Description

Languages

Verilog

50.2%

C

43.9%

Makefile

5.2%

Shell

0.6%

SystemVerilog

0.1%